核心总结 (Key Takeaways)

- 超长寿命:10万次擦写次数,确保工业设备10年以上稳定运行。

- 低功耗设计:1.8V电压供电,显著延长手持终端续航时间。

- 设计避坑:WP#引脚必须硬件级管理,防止系统上下电数据丢失。

- 灵活替代:涵盖国产化及SPI NAND方案,平衡成本与供应链安全。

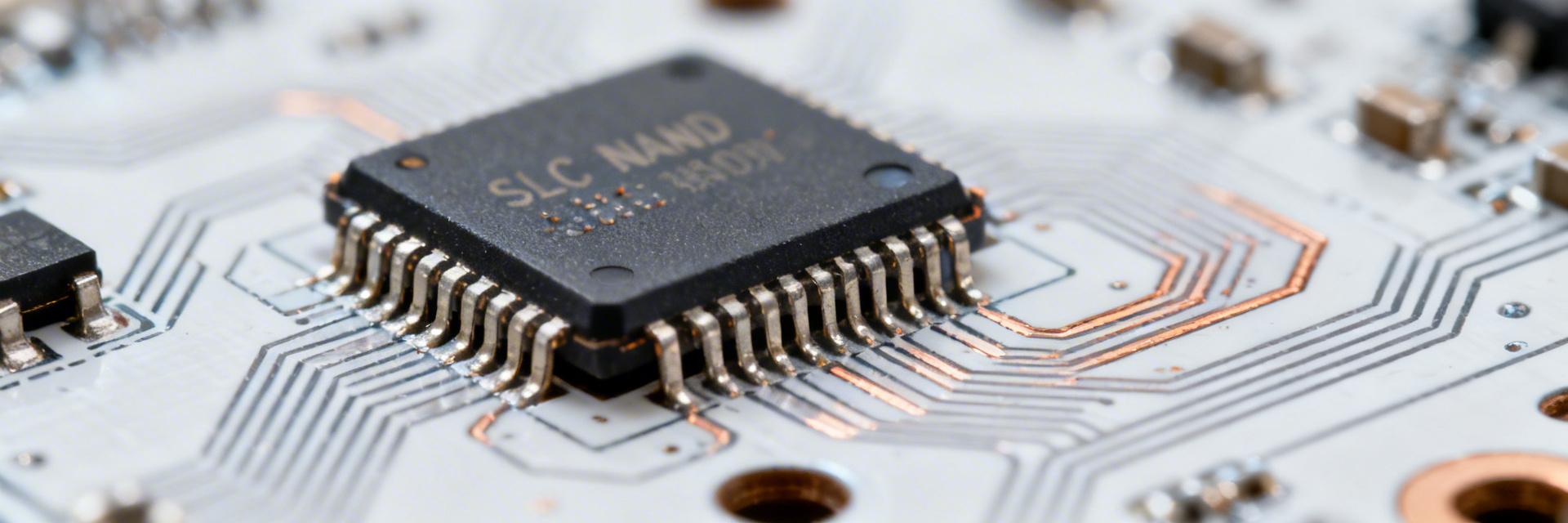

在工业控制与嵌入式设备领域,对数据存储的可靠性要求日益严苛。SLC NAND Flash凭借其高耐用性和稳定性,依然是关键应用场景的首选存储介质。其中,TC58NVG1S3ETAI0作为一款经典的2Gb SLC NAND芯片,其设计细节与选型考量至关重要。本文将深入解析其核心规格演变,揭示PCB布局中的引脚设计陷阱,并为工程师在当前市场环境下提供更具成本效益的可靠替代方案。

核心规格深度解析与横向对比

比3.3V型号降低约45%功耗,有效缓解密闭外壳内的散热压力。

高频率数据记录场景下,设备维护周期比普通MLC延长5-10倍。

TC58NVG1S3ETAI0是一款采用1.8V电压供电的2Gb(256MB)SLC NAND闪存芯片,以其在严苛环境下的数据保持能力和高擦写次数而闻名。理解其规格的细微之处,是确保系统长期稳定运行的基础。

从TC58NVG1S3ETA00到ETAI0:关键参数演进

工程师在选择TC58NVG1S3ETAI0时,常会注意到其与早期型号如TC58NVG1S3ETA00的关联。ETAI0型号在内部工艺上进行了优化,以适应更广泛的工业温度范围(-40°C到85°C)。因此,直接替换时,必须仔细核对数据手册中的交流特性,避免系统初始化失败。

主流SLC NAND性能基准对比

| 对比维度 | TC58NVG1S3ETAI0 | 行业通用款 (1.8V) | 高性价比替代方案 |

|---|---|---|---|

| 页大小 (Page Size) | 2K + 64 Bytes | 2K + 64 Bytes | 2K + 128 Bytes (纠错更强) |

| 读取延迟 (tR) | 25μs (典型) | 30μs | 20-25μs |

| 待机电流 | 10μA (极低) | 50μA | 20μA |

| 成本优势 | 中等 (原厂品质) | 较高 | 可降低 15-25% |

引脚功能详解与PCB布局避坑指南

TC58NVG1S3ETAI0通常采用TSOP48封装,其引脚排列需要工程师格外关注。

“在处理TC58NVG1S3ETAI0的PCB设计时,最容易忽视的是VCCQ的去耦布局。很多新手直接将电容放在背面过孔处,这在高频读取时会导致严重的信号完整性问题。建议将0.1μF电容放在同层且距离引脚2mm以内。另外,WP#引脚千万不要直接拉高,必须通过主控GPIO控制,以防系统掉电时的误操作。”

典型应用布局建议

布局核心:

1. 走线等长:I/O0-I/O7 数据线误差控制在50mil以内。

2. 地平面:芯片下方必须有完整的地参考平面,禁止走线切割。

3. 防护:在WP#和CE#线上增加RC滤波,抑制瞬态毛刺。

3大高性价比替代方案全面评估

鉴于元器件供应链的动态变化,为TC58NVG1S3ETAI0寻找可靠替代方案至关重要:

- 方案一:同品牌工艺升级款

硬件改动最小,仅需在驱动层确认上电Reset时间(tRST)是否兼容。 - 方案二:国产化高性能兼容品

在电力、轨道交通领域已有大规模应用,成本可降低约20%,且供货周期更稳定。 - 方案三:SPI NAND 架构转换

如果PCB空间受限,建议改用8引脚的SPI NAND,虽然需要重写驱动,但能节省60%以上的布线面积。

常见问题解答 (FAQ)

Q: TC58NVG1S3ETAI0的ECC要求是多少?

A: 该芯片通常要求 1-bit ECC per 512 bytes。但为了提高长期可靠性,建议主控端开启 4-bit 或更高的硬件 ECC。

Q: 1.8V 和 3.3V 版本可以互换吗?

A: 绝对不可以。物理电压不匹配会烧毁芯片或导致系统无法上电。请务必检查 BOM 列表中的电压后缀。