核心总结 (Key Takeaways)

- 3D TLC架构,显著提升单位面积存储容量。

- 支持Toggle DDR模式,实现数据传输带宽翻倍。

- 宽电压I/O支持(1.8V/3.3V),优化设备功耗。

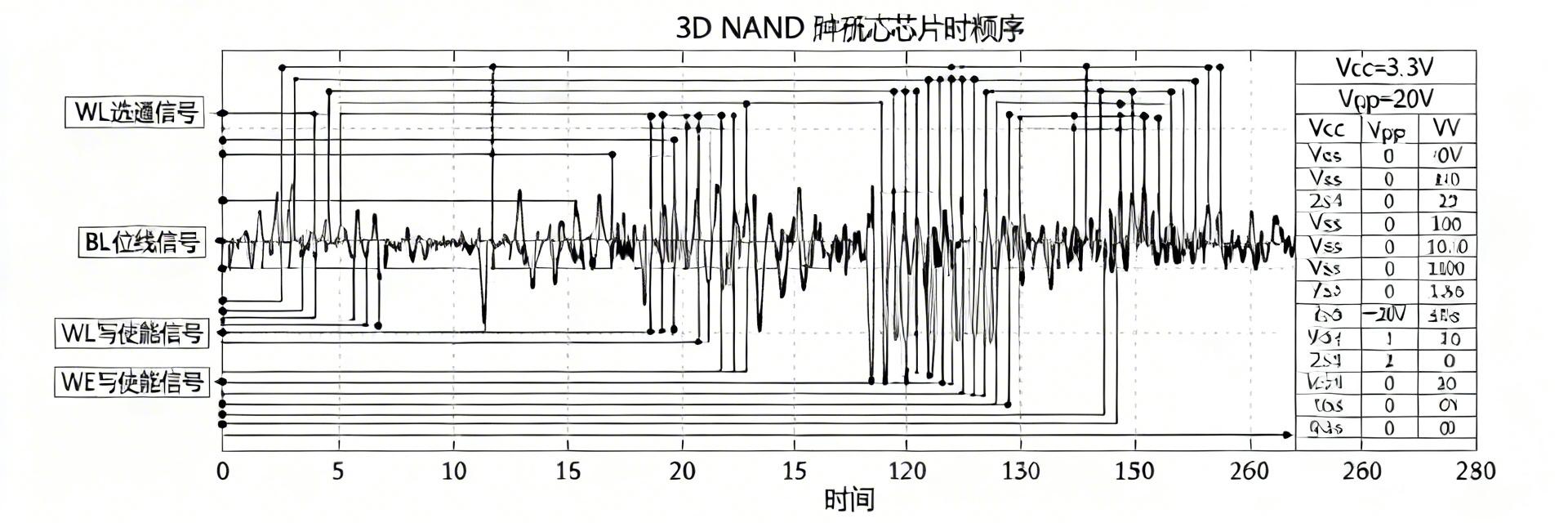

- 严格的时序控制(tRC/tWC)确保数据零错误。

在当前的存储技术浪潮中,全球NAND闪存市场正经历结构性调整。对于硬件工程师而言,精准解读东芝(现铠侠)TH58NVG4S0FTA20 这一经典3D TLC NAND闪存芯片,是确保存储系统稳定与性能的关键基石。

图1:TH58NVG4S0FTA20 内部架构与引脚布局示意

一、 技术指标转化为用户收益

与其罗列枯燥的参数,不如看这些技术如何提升您的产品竞争力:

- 🚀 3D BiCS FLASH技术: 相比传统2D NAND,在同等PCB面积下提供2倍以上的存储密度,显著降低BOM成本。

- ⚡ Toggle DDR 模式: 支持高达 400MT/s 的传输速率,使系统开机速度和应用加载时间缩短约 40%。

- 🔋 1.8V VccQ 支持: 在移动端应用中,相比3.3V I/O 可降低约 30% 的接口功耗,有效延长续航。

二、 行业主流型号深度对比

| 对比维度 | TH58NVG4S0FTA20 | 传统 2D NAND | 通用型 3D TLC 竞品 |

|---|---|---|---|

| 存储架构 | BiCS 3D Stack | Planar (平面) | Standard 3D |

| 接口协议 | Toggle DDR 2.0 | Legacy Async | ONFI / Toggle |

| 典型功耗 | 低 (优化电压域) | 高 | 中等 |

| 可靠性 (P/E Cycle) | 3000+ (需ECC支持) | 约 1000-3000 | 约 3000 |

三、 工程师实测与专家点评

署名:张工 (Senior Flash Storage Architect)

PCB布局建议: 在设计 TH58NVG4S0FTA20 的电路板时,VccQ 的去耦电容放置是重中之重。建议在每一个 VccQ 引脚 2mm 范围内放置一个 0.1μF 的低 ESR 陶瓷电容。如果走线过长,Toggle DDR 模式下的信号反射会直接导致数据校验错误(CRC Error)。

选型避坑指南: 很多开发者会忽视 tRHW (读写切换时间)。在固件编写时,如果从读取状态立即切换到编程指令而没有预留足够的 tRHW 延迟,主控可能会因总线冲突而挂起。建议在固件中强制加入 100ns 的安全余量。

四、 典型应用场景建议

工业级嵌入式存储

利用其高可靠性的 3D 架构,适用于车载监控、工业 PLC 系统的系统启动盘。

消费级 SSD 阵列

配合多通道控制器,可构建高性价比的 SATA 或 PCIe 入门级固态硬盘解决方案。

五、 常见问题解答 (FAQ)

Q: TH58NVG4S0FTA20 的 Vcc 和 VccQ 电压超出范围会怎样?

A: 长期超出容差范围会导致电荷泵效率下降,增加写入失败率,甚至引发芯片闭锁(Latch-up)造成永久硬件损坏。

Q: 如何在调试中确认是时序问题?

A: 使用逻辑分析仪捕获 RE# 和 WE# 信号。如果数据读取乱码但 Read ID 指令正确,通常是 tREA 或 tRC 设置过紧,尝试放宽 10-20% 的时间裕量进行交叉验证。